源内CADの質問コーナーに、よく「非同期7進カウンター」とか「非同期6進カウンタ」とかってコトバを見かけます。

論理回路のお勉強用として、またはパズルとしては良いかと思うのですが。。。。

現実世界では、非同期カウンタは(2のn乗)進カウンタ以外にはありえません。

ガッコで非同期7進カウンタを勉強したからと言って、それを量産品設計に使うと、たちまちトンデモナイ目に会いますので、ご注意を。

|

なんでかって?

非同期のハンパ数カウンタってのは、必ず「計算できない幅のパルスを使うコトになる」からです。

全ての信号が計算可能なパルス幅を持つようにで設計できていれば、非同期ハンパ数カウンタもOKです。

けど、そんな回路を組める人なら、サクッと同期カウンタを作ってしまいます(^^;

|

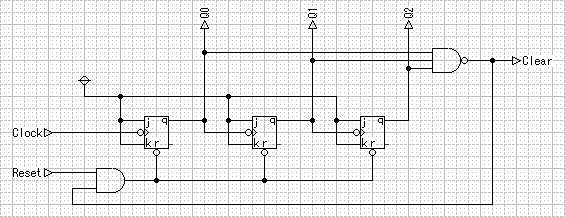

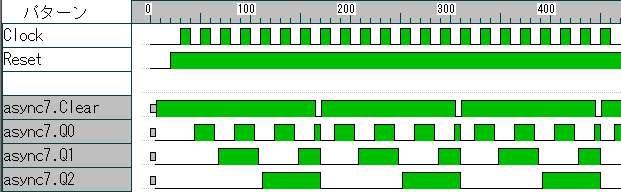

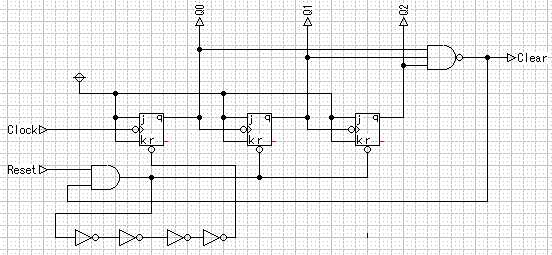

例えば、源内CAD質問コーナーの回答として、下記の回路の「非同期7進カウンタ」が載っています。

これ、シミュレーションかけると、たしかに動きます。

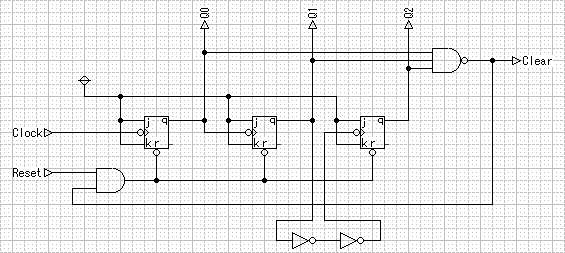

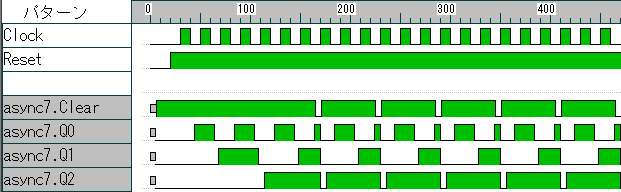

けど、この回路図にインバータを2個追加します。

インバータ2個直列ですので、先の回路と論理は変わっていません。

にもかかわらず、シミュレーションすると動作がヘンになります。

あークロックを遅延させるのは反則に近いかな、同期回路でもクロック遅延させたら動かないモンねぇ。

じゃ、別なトコにインバーターを4ヶ。この回路、インバータ2ヶだと動いてしまったんで(^^;

これって、「どっかのFlipFlopの出来が悪い(遅延時間が長い)とか、「どっかの配線が長い」とか、そーゆー要因があるともう回路は動かないってコトです。

だから、非同期ハンパ数カウンタみたいな、微妙なタイミングで動く回路を設計して、「シミュレーションで動いてるから・・」と言ってICとかでソノママ作ると、運の良い人と運の悪い人に分かれます。

(LSIで作るんだったら、LSI製造用CADが「こりゃアカン」ってエラー出すので、LSIを作れません(^^;)

|

大吉な人 |

いつでもドコでも何度でも何台つくっても、ちゃんと動作する人。 |

|

| 吉な人 |

作ってみたけどちゃんと動かないので、同期カウンタに設計変更した人。 |

| 凶な人 |

動作確認の時には正常動作するのに、先生に動作を見せる時に鍵って動かない人。 |

| 大凶な人 |

試作100台作って全部正常動作したのに、10万台量産したら1万台ほど動作不良品が出来た人 |

|

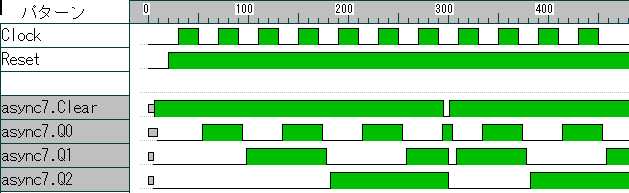

回路のどこに問題があるかってぇと、タイミングチャートの中の2箇所に見える幅の狭いパルス、Clear信号の'0'レベルパルスと、Clear信号が'0'になる瞬間のQ0信号の'1'レベルパルスです。

これらのパルスは、ゲートやFlipFlopの遅延時間ダケでパルス幅が決まっています。

んで、論理シミュレータ上のゲートやFlipFlopは、遅延量が一律で決まっていて変動したりしませんから、シミュレータ上では安定して動きます。

しかし、現実世界のゲートやFlipFlopは、ICの出来具合や温度電圧、出力負荷容量やら配線の長さで、遅延時間は変動します。

ちなみに「出力が'0'から'1'に変化する場合と、'1'から'0'に変化する場合とで、遅延時間が異なる」なんて、現実世界では常識です。

そのような現実世界で、この回路が安定して動きますか?

|

こゆの、慣れると簡単に見つけるコトが出来て、見るポイントは こゆの、慣れると簡単に見つけるコトが出来て、見るポイントは

- 回路の動作基準となるクロックよりパルス幅が狭い信号は、あやしい。

- クロック1周期の中で2回以上変化する信号は、あやしい。

- そういうあやしい信号を使っているFlipFlopがあると、もうムチャクチャあやしい。

- あやしい信号があっても、それが伝達しなければ、問題はない。

もっと簡単に、

- ゲートで作った信号がFlipFlopのクロックに繋がっている回路は、あやしい。

- 定期的に発生するパルスがFlipFlopのセットまたはリセットに繋がっている回路は、あやしい。

そういう回路を排除するために出来たルールが、「同期設計」です。

同期設計を理解していないと、現実世界で論理回路設計は出来ないと思ったほうが良いでしょう。

まぁ同期設計を理解するためには、同期4bitカウンタくらいはご飯食べながらでも書けるくらいの知識が要りますが。。。

|