12時間または24時間デジタル時計(時、分、秒)の表示データを出力する論理モジュールであって、時計を止めることができて、目覚まし時計の機能があるものを作りましょう。

この質問、源内CADの質問コーナーに2004年06月05日にアップされており、かつ「単位を落としそうです」というコメントがありました。

質問のスタンスが、「どの部分が判らないからココだけ教えて」ってな内容ではなく、ゼロから10まで教えてくれ、あるいは直接答えをくれ、っていう内容だったので、当然これまで回答無しでした。。。単位は大丈夫だったのでしょうか? 質問のスタンスが、「どの部分が判らないからココだけ教えて」ってな内容ではなく、ゼロから10まで教えてくれ、あるいは直接答えをくれ、っていう内容だったので、当然これまで回答無しでした。。。単位は大丈夫だったのでしょうか?

さてこのコーナーは源内CADの公式サポートページではなく、「ひとりのヒマ人が源内CADのQ&Aコーナーをネタにして、好き勝手に回答モドキを書いている」っていうスタンスですので、質問に対する素直な回答ではなく、「ギリギリ自力で上記の時計を作れる人がより複雑な問題を解けるように」なるためのヒントを書いておきます(^^;

|

まず例によって機能分析、兼、必要パーツの分析。。

| 要求機能 |

必要なパーツ |

解説あるいは世迷い言 |

とにかく時間を

カウントする |

クロック入力 |

論理回路が自動で何かの動作を継続する場合、たいていクロックが必要です。論理回路では、クロックの分周は出来ますけど、クロックそのものの生成は出来ませんので、適当なクロックが外部から与えられると考えましょう。

今回は時分秒をカウントできれば良いってコトなので、分周とか余計なモノが要らなくなるように、1Hzのクロックが入力されるものと、勝手に想定しますw |

| 秒をカウントする |

6bitの60進カウンタ |

1Hzのクロックを使って、秒をカウントします。

秒のカウント範囲は0秒から59秒までですので、60進カウンタになります。

カウンターのbit長は、2^6=64>60で、6bitになります。 |

| 分をカウントする |

6bitの60進カウンタ |

秒カウンタのケタ上がりを使って、分をカウントします。

分のカウント範囲は0秒から59秒までですので、60進カウンタになります。

カウンタのbit長は、2^6=64>60で、6bitになります。 |

| 時をカウントする |

5bitの24進カウンタ |

分カウンタのケタ上がりを使って、時をカウントします。

時のカウント範囲は0秒から23秒までですので、24進カウンタになります。

カウンタのbit長は、2^5=32>24で、5bitになります。

作るデジタル時計は、12時間制か24時間制かドッチでも良い見たいなので、勝手に24時間制と決め付けますw。

ま、ヒマな人は12時間制と24時間制を切り替えられるように考えて見てちょw |

年月日を

カウントする |

(そういう機能はナシ) |

時分秒のカウントは楽なんですが、年月日のカウントはめちゃタイヘンです。

だって、月によって日数が違うし、たまーに閏年ってのがある。

あーそういえば閏秒ってコトバもあったなぁ、、今は忘れておこうw |

| 時計を止める |

? |

「時計を止める」ってのは解釈が微妙です。時分秒のカウント自体を止めるのか、それともカウントは止めずに表示が更新されないようにするだけなのか。。。。

これは、何のために止めるのか、または出題者がどういう意図を持っているか、を汲み取って考えねばならないのですが、モトとなる質問文からは読み取れないので、「表示の更新を停止する」というカタチに勝手に考えます。 |

カウンタを止めずに

表示の更新を

停止する |

計17bitのFlipFlop

時計停止信号入力 |

時分秒をカウントするカウンタは止めずに表示の更新を停止するっていう機能に定義しちゃったので、カウンタとは別に表示時刻を保持するFlipFlopが必要になります。時に5bit、分に6bit、秒に6bit、計17bitのFlipFlopが必要です。 |

| 目覚まし機能 |

目覚まし時刻データ入力

目覚ましパルス出力

17bitコンパレータ |

目覚まし機能ってのは、たいてい、指定した時間に何かの動作をするって機能です。音を鳴らすにしろ、TVの電源をONにするにしろ、バクハツするにしろ(←こゆのは目覚ましじゃなく時限爆弾って言う)、論理回路が扱える範疇を超えますw

論理回路で扱える範囲の目覚まし機能として、目覚ましを鳴らすべき時刻データを外部から入力して貰い、入力される目覚まし時刻データと、内部にある時分秒カウンタの出力が一致した時にパルスを出力するっていう機能に定義します。

目覚まし時刻データとして、時に5bit、分に6bit、秒に6bitの外部入力が必要です。

目覚ましパルスとして、1bitの出力が必要です。

入力される目覚まし時刻データと、内部にある時分秒カウンタの出力が一致しているかどうかをチェックするコンパレータが必要です。 |

| 時刻データ出力 |

時刻データ出力 |

時に5bit、分に6bit、秒に6bitのデータを出力します。 |

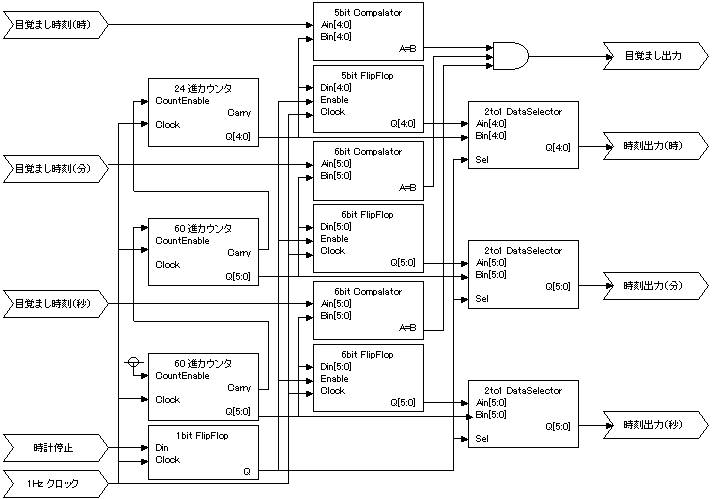

上の表が出来たら、もうほとんど完成。あとは、見繕ったパーツを適当に並べて、線でつなぐだけ。

実際にやってみると、下図のようになる。ってか、下図の構成ダケが正解ではないので、「僕の場合は下図のようになりました」って表現が適当ですw

この図の書き方は、自己流です(^^;

ガッコや会社で標準的な書き方が在る場合には、それに従いましょう。

書式はどうであれ、こういう図を書く時のコツは、

- 使用するパーツは、パーツ名と端子名から類推できるもっとも単純な機能にすること。

パーツ名とパーツの端子名は、機能を類推できる名前にすること。

各パーツに特別な機能を要求すると、この図を書くときには覚えていても、各パーツの内部回路を作るときには既に忘れていて、結果として回路が動かない。。。ってコトになりかねません。

また単純なパーツばかりにしておくと、パーツ単位で他の回路に流用できます。

- 必要な外部入出力、必要なパーツ、各パーツの端子を全て書くこと。

書いておかないと、あとで機能が足りないとか、機能通りの動作にならない、ってコトになります。

- 全体も各パーツも、左側が入力で右側が出力になるよう、統一する。

そう統一しておかないと、図の中に入出力の区別を書き込まなくちゃイケナくて面倒くなるし、各パーツを作る時のカンチガイも増えます。

- 図面上で十字結線は行わないこと。

十字結線を使っていると、図面を見せた人に「はは〜んコイツ素人だな」と思われてシャクに触りますw

この図がしっかり書ければ、この図で誤りチェックや機能不足がないかをチェックできる。 この図がしっかり書ければ、この図で誤りチェックや機能不足がないかをチェックできる。

仕事で回路を組む場合には、有識者に見せて指導を仰ぐ、または皆で集まってレビューすることが出来る。

この図の段階で誤りチェックをシッカリやれば、後になって間違いが見つかってハジメカラヤリナオシってな無駄を防げる。

回路構成を簡単に説明すると、

- 図の左端に外部から入力されるべき信号が記されています。

- そのすぐ右側に、上から時をカウントする24進カウンタ、分をカウントする60進カウンタ、秒をカウントする60進カウンタが並んでいます。

一番下の1bitFlipFlopは、時計停止信号を1Hzクロックに同期させるためのD-FlipFlopです。時計停止信号が1Hzクロックと非同期の信号である場合にこのFlipFlopを忘れると、シミュレータ上ではカンペキに動作しても、実際の回路で時々バグる、っていう悲惨な目にあいます。。。。。何度そういう目にあったコトか。。

- 真ん中の列には、時計停止時にカウンタを動かしながら表示データを保持するためのFlipFlopと、目覚まし機能のためのコンパレータが並んでいます。

コンパレータの綴りは、もしかしたら違っているかも、、、です(^^;

- その右側には、時分秒カウンタの値を出力するか、それとも時計停止機能用FlipFlopの値を出力するか、を選択するセレクタが並んでいます。

セレクタの内部回路を組む時には、SEL入力の値と出力する信号との対応に気をつけてください。ここ適当に組むと1/2の確率でバグるんですが、過去の経験から、こういう1/2のバクチの勝負はたいてい負けます(^^;

- 一番右側は出力信号です。

- なお、図中の各信号線は全て正論理で、クロックを使う回路は全て立ち上がりエッジ動作です。

この図を書いて、誤りチェックを行ったら、あとは各パーツの中身を作って組み合わせればOK。各パーツは単純な機能にしてあるハズだから、カンタンだよね?w

回路を作る際に、こういう図をサラリと書けると、回路を作って一発で動作させられる可能性が非常に高くなります。

もっと慣れると、作る回路の説明を聞いているウチから、この図のイメージが頭の中に勝手に出来上がりますw

|

この絵を見て、「秒をカウントする60進カウンタに、何でCountEnableがあるの?」とか思った方。あなたは鋭い。

これは、同じ60進カウンタのパーツを、分カウント用の60進カウンタと、秒カウント用の60進カウンタの両方に使用するためです。

こうしておくと、パーツを1個作る手間が省けます。

|

この図では時計停止機能にFlipFlopとDataSelectorを使っているけど、「スルーラッチを使えば1発なんじゃないの?」とか思った方。あなたもまた鋭い。

LSI化またはFPGA化する回路の場合、スルーラッチを使ってはイケマセン。スルーラッチは同期設計のルールから外れますので、後でいろいろとヤヤこしい問題が湧き上がってきます。素直にFlipFlopにしときゃヨカッタ〜って絶対思いますw

74xxシリーズとかのロジックICを使用して回路を実現する場合、ICの数が減るのでスルーラッチはオススメです。

でも、スルーラッチを使うとたぶん、入力クロック周波数が1Hzじゃシンドイかと思います。何がシンドイかって、カウンタの出力が安定している瞬間にスルー状態からラッチ状態に変化させにゃならんくて、このタイミングを作るのに立下りエッジとかゲートディレイとか・・・ま、おヒマな方はやってミソ(^^;

|

「時カウンタのCountEnableって、分カウンタのケタ上がりと秒カウンタのケタ上がりのAND条件で動く必要があるんでないの?」とか思った方。あなたはカナリ鋭い。

そのとおり、時カウンタがカウントアップすべきタイミングは、分カウンタの値が59で、かつ秒カウンタの値が59の時ダケです。

ま、これは60進カウンタのパーツの作り方で逃げるコトが出来て、CountEnableの条件を含めてCarry出力を生成してくれれば、それでOKです。

この方法、クロック周波数が高くてカウンタの段数が増えると、信号伝達が間に合わないって問題がおきます。

今回は、お絵かきソフトでANDゲート書くのが面倒だったので、そういうコトにしておきました(^^;

|

「この図の目覚まし出力じゃ、ハザードが出るんじゃないの?」とか思った方。あなたはメチャンコ鋭い。

この部分は書くのがめんどかったので、大幅に手抜きしてあります(汗)

この図のままだと、「目覚まし時刻になった時に、1秒間だけパルスを出力する」という仕様になっており、さらに「目覚まし時刻になっていなくても、時々ノイズっぽい短いパルスが出力されてしまう」という問題を含んでいます。

実際には、この目覚まし出力の信号の先に、さらに論理回路を追加して、必要な目覚まし動作を実現することになります。

|

「時計停止信号がアサートされている間、時計停止機能用FlipFlopのEnable端子がアサートされっぱなしになって、時計停止機能が働かないんでないの?」とか思った方。あなたはすんごい鋭い。

はい、そのとおり、この図ではバグっています(^^;

時計停止信号を1Hzに同期させる1bitFlipFlopの後に、もう1個1bitFlipFlopをp追加して、立ち上がり微分しなくっちゃ。。。

こういう間違いを早い段階で見つけるために、こういう図が必要なワケさ。これを説明したかったから、ワザとバグった図を載せたんだよ〜、え〜ホントだよ〜(汗)

|

で、実はこの時計、もっともーーーーっと致命的な欠陥があっちゃったりする(^^; で、実はこの時計、もっともーーーーっと致命的な欠陥があっちゃったりする(^^;

それは・・・・時刻あわせの機能が無い!

時計として使うためには、0時0分0秒に回路動作を開始させてくださいませ・・・・って思うのはまだまだアサハカ。

実際の論理回路は、電源投入時の各FlipFlopの値は不定だから、この時計回路が動作開始時に0時0分0秒になるとは限らない。。リセット信号を用意しなかったからねぇ(^^;

だから、この時計回路は、現実には全く使えないw でも最初の機能定義に時刻あわせ機能なんて書いてなかったんだもん、しょうがないよね(^^;;;;

|