「5入力+CLK⇒1出力の同期式多数決回路を、加算回路を使って設計せよ。」 「5入力+CLK⇒1出力の同期式多数決回路を、加算回路を使って設計せよ。」

うん、この質問は判りやすい。

けどこの質問の後ろに、カッコ付きでこんな注釈が付いている。

「厳密には、すべて2NAND回路で組むことになっています」

はて、これは途方もなく難儀だ。。。。

なにが難儀かってぇと。

- 設問にわざわざ「同期式」って書いてあって、クロック入力まで定義されているんだから、FlipFlopは登場して欲しいだろぉ。

でも回路は全て2入力NAND。。。ってコトは、まず、2入力NANDを使ってFlipFlopを組まなきゃイケナイのかしら。。。

- 設問にわざわざ「加算回路を使って」って書いてある。

ってコトは、加算回路も2入力NNADで組まにゃイケナイのかしら。。。。

いや、どちらもきっと、やろうと思えば出来るんだろうけど、今更FlipFlopとか加算回路を2入力NANDで組みなおすのは、面倒だ(^^;

というワケで、この質問についても素直な回答じゃなくって、好き勝手回答にしてしまおう(^^;

|

まず「多数決回路」って何だろうねぇ。 まず「多数決回路」って何だろうねぇ。

たぶん「複数の1bit入力があって、その複数の1bit入力に与えられる'0'または'1'の値のうち、数の多い方の値を出力とする」ってな回路のコトだと思う。

じゃ「同期式」っていうマクラコトバが付くと、どうなるんだろうねぇ。

たぶん「時間を離散化させよ(論理回路って、なんですか?を参照のこと)」って意味だと思う。

具体的に言うと、「クロックの立ち上がりエッジが発生した瞬間の入力の値を使って、多数決の答えを出せ」って意味だと思う。

「加算回路を使った多数決回路」ってどんなんだろうねぇ。

って言うか、多数決回路は加算回路を使えばカンタンに出来てしまう。

だって、、、、(2n-1)個の入力を持つ多数決回路の場合、入力を全部加算して、その結果が(n)以上か(n)未満かで多数決の答えが出てしまう。

この設問だと5入力なんだから、5個の入力に与えられる'1'または'0'の値を全部加算して、加算結果が3以上なら'1'の勝ち、3未満なら'0'の勝ち、ってコトになる。

| 入力#1 |

入力#2 |

入力#3 |

入力#4 |

入力#5 |

加算結果 |

多数決結果 |

| 0 |

0 |

0 |

0 |

0 |

0+0+0+0+0= 0 |

'0'の勝ち |

| 1 |

0 |

0 |

0 |

0 |

1+0+0+0+0= 1 |

'0'の勝ち |

| 1 |

1 |

0 |

0 |

0 |

1+1+0+0+0= 2 |

'0'の勝ち |

| 1 |

1 |

1 |

0 |

0 |

1+1+1+0+0= 3 |

'1'の勝ち |

| 1 |

1 |

1 |

1 |

0 |

1+1+1+1+0= 4 |

'1'の勝ち |

| 1 |

1 |

1 |

1 |

1 |

1+1+1+1+1= 5 |

'1'の勝ち |

|

ちと脱線するけど、入力の数が少なくて、あとで設計変更が発生しないんなら、AND+ORでも同じ回路が作れてしまう。

(AND+OR)ってコトは、NAND+NANDでも作れるってコトだけど・・)

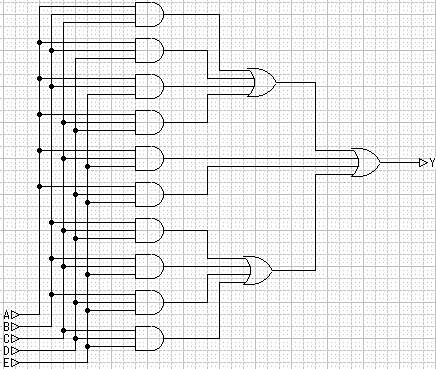

とりあえず式で書くと、こうなる。

| 非同期5入力多数決 = (A and B and C) or (A and B and D) or (A and B and

E) or (A and C and D) or (A and C and E) or (A and D and E) or (B and C

and D) or (B and C and E) or (B and D and E) or (C and D and E) |

この式の意味を簡単に言うと、A〜Eの5入力のうち、任意の3つが'1'だったら答えは'1'ってコト。

回路にすると、こうなる。

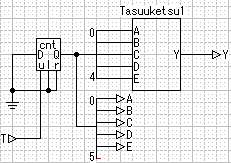

回路が出来たらシミュレーションで機能確認するんだけど、入力パターンを網羅的に書くのがカッタルイよねぇ。

こういう場合、入力パターンを生成する回路を作って、この回路と組み合わせてシミュレーションしちゃう(^^;

入力パターンを生成する回路って言っても、カウンタ1個だけどねぇ(^^;

右上の「Tasuuketsu1」っていう箱は、上に書いたAND-ORゲート構成のロジックを部品化したものです。

これシミュレーションかけると、こうなる。

A,B,C,D,Eは、このシミュレーション結果の出力だけど、ホントにシミュレーションしたい部分にとっては入力だからね(^^;

さて、ちゃんと多数決が取れているかね?

あれカウンタをリセットするのを忘れてる。。。ま、動いてるみたいだからイイや(^^; |