さて、えーと、問題はNOR×2ヶ+OR×1ヶだったんだけど、、AND×1ヶになっちゃったよ、どーしよう(^^; さて、えーと、問題はNOR×2ヶ+OR×1ヶだったんだけど、、AND×1ヶになっちゃったよ、どーしよう(^^;

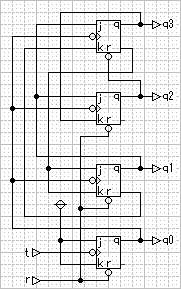

FlipFlopの反転出力使って、(Q1 and Q2)を(QC1 nor QC2)って変換すればNOR×1ヶになっちゃうから、あとNORとOR各1ヶは、どっか邪魔にならないトコに置いといて(^^;

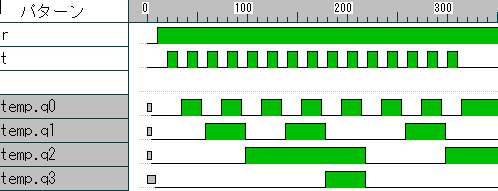

ちなみにこの回路、非同期のハンパ数カウンタでありながら、計算できない幅のパルスを使っていない。

そのヒミツは、非同期なのはQ0とQ1〜Q3との関係ダケであって、Q1〜Q3部分は同期5進カウンタになってるコト。

同期・非同期みっくちゅカウンタだわ。

回路全体が完全同期じゃぁないから、LSIやFPGAでは使わないほうがいいけど、汎用ロジックで回路組むんなら十分使えるかもねぇ。

|

| まとめw |

結局、問題文の構成のカウンタは出来ていない。

同期カウンタであれば、JK-FF×4ヶ+AND×4ヶまでイケた。

同期カウンタの条件(単一クロック単一クリア)の範囲内では、これ以上のゲート削減は出来そうに無いんで、

正解はきっと同期カウンタから外れたカウンタなんだろうと推定。

で、非同期カウンタの世界に入れば、問題文よりゲートの少ない回路が出来た。

なんてったってFlipFlop以外に使うのはANDが1ヶダケだ。

さらにゲート削減するとFlipFlopダケしか残らない(^^;;;; だからこれ以上考えるのは不毛だぁ。。。

ヒキョーな方法として、4bitカウンタでありながらJK-FFを5ヶ以上使うって手があるけど。。。

いくらFlipFlopの数は指定されてないと言っても、なんぼなんでもあづましくないよねぇ。。。(←北海道弁?)

|

| 不毛なカウンタが出来てしまった。。。 |

不毛だぁとか言いながら、ほけら〜っと考えてたら、出来てしまった。

JK-FF×4ヶ+ゲート×0ヶ。。。。

カウント値はオカシいけれど、ちゃんと10クロック周期で動いてる。

ああ、むなしい。。。

|

| あとがきの続き。。。 |

まぁ、もしかしたら、回路の動作条件の考え方を変えれば、同期カウンタで問題文の構成のが作れるのかもしれない。

今回はT-FFを基本として、各bitの反転条件を考えるトコからスタートしたけどね、別な考え方のカウンタをベースにすれば、違った答えに行き着くかもしれない。

これはこれで楽しいパズルだと思うんで、やってみてちょ。

たぶん「NORを2ヶ使う」ってのがヒントになると思う。

NORっては正論理入力負論理出力のORだけど、負論理入力正論理出力のANDと等価だよね。

でも負論理入力はFlipFlopのQC出力使えば不要なんで、NORはやっぱNORで使うんだろう。

このNORの負論理出力を、10進カウンタの動作条件の中で、どう使うか。きっとこれがヒントだよw

もしくは、74xx390っていう標準ロジックICの内部回路が参考になるかもしれない。

74LS390は、T-FFを使って、各FlipFlopに入力されるクロックを制御して各bitの反転条件を作ってる。

けど、74xx390の内部回路は、パズルとしては楽しいけれども、LSIやFPGAの回路としては全く実用にならないので、

見ないほうが幸せかもしれない。。。。

|

| 蛇足(^^; |

ちなみに、「〜という問題なんですが、考えても判りません」ってパターンの問題は、なかなか答えようという気が起きないんだよね。

ボクも量子力学とかの問題になると、そういう質問したくなるんだけどね(^^; アタマが考えるのをキョヒするんだよね(^^; ボクも量子力学とかの問題になると、そういう質問したくなるんだけどね(^^; アタマが考えるのをキョヒするんだよね(^^;

それは、応用問題を解けるほど基礎を理解してないからなんだよね(^^;

マジメに考えるために質問を書くんなら、漠然とした聞き方しないで、 「こんなん作ってみたんだけど上手く動かない」とか、「自分で作るとどーしてもNANDが必要になっちゃうんだけど・・」とか、

そういう書き方すればピンポイントで回答がもらえる。

それが出来ない時は、基礎からガンバりましょう(^^;

|